|

第7回:IEEE 802.11a対応無線カード(後編) | ||||||||||||

|

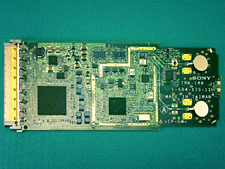

前回、誌面の都合で分解編までをお送りした。今回は細かな内部構造に移ろう。 ■内部構造(構造編)

ではいよいよ細かな内部構造に移る。現時点でIEEE 802.11a向けに量産出荷し、かつ最終製品が入手できるものは米Atheros CommunicationsのAR5000シリーズしか存在しない。この製品の特徴は以下のようなところだ。

ちなみにAR5000シリーズも実際にはいくつかある。

ちなみに今回のWN-A54/PCMは、第一世代のAR5000を利用したものだ。

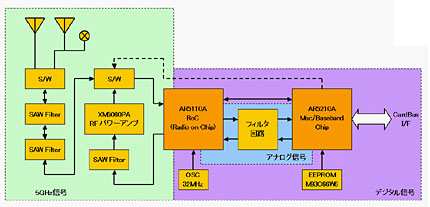

さて、全体の構成は<図1>に示すとおりだ。全体は大きく2つのブロックに分かれる。まずIEEE 802.11aの信号を取り扱う5GHzの信号部だ。写真右の、シールドに囲まれた部分は直接5GHzの信号を取り扱う部分だ。右側のアンテナ部から入った信号はそのままシールド内部のRF部に送り込まれ、ここでダイレクトに5GHzの信号はI/Q信号に置き換えられる。 そのI/Q信号はシールドの左側にあるMAC/ベースバンドチップに入り、ここでデジタル化され、CardBusインターフェイス経由でPCに送り込まれるという具合だ。以前のIEEE 802.11bカードに比べると非常にシンプルになっているが、これはチップ外部に中間周波数が一切出ないことと、チップの集積度が上がったことが関係している。その証拠に、IEEE 802.11bカードは裏面までびっしりとチップが搭載されていたのに対し、WN-A54/PCMでは片面実装で済んでいる。このあたりが、回路の進化ぶりを実感させてくれる。

■内部構造(パーツ編) 以上、大雑把にIEEE 802.11bカードの動作ブロックの説明を行なったところで、それでは個別の説明に移ろう。 【アンテナ部】

ご覧の通りの円形アンテナ。ちょっと面白いのは、アンテナの周囲にグランドどのビアホールが取り囲むように配置されていることで、しかもその配置が微妙に異なっていることを見ると、これによって偏波ダイバーシティの効果を得られるのかもしれない。また右側のアンテナの方の先には、明らかに外部アンテナ用と思われるコネクタが用意されており、ケース側に対応を施せば外部アンテナが接続可能になるらしい。なお、そのコネクタの横にあるICは紛らわしいが、とりあえずアンテナ部とは一切関係ない。 【RF部】

図で、「5GHz帯」と記してある部分からアンテナを除いたのがここだ。右端にあるのが村田製作所の5.2/5.8GHz帯用パワーアンプであるXM5060PAである。AR5110はスペック上、RFパワーアンプを内蔵しており、IEEE 802.11aでは外部アンプが必要ないことになっている筈なのだが、実際はそこまでの出力が取れないらしい。 この結果、外部にパワーアンプを装備しないと十分な信号強度が確保できなかったという話を聞いたことがあり、実際回路構成はそのようになっている。実際これを予想してか、AR5110は"Extra PA(Power Amplifire) and LNA(Low Noise Ampulifire) can be used for special application"という但し書き付きで外部PAを利用できるようになっている。ちなみに第2世代以降ではこのあたりが随分改善されたらしい。 その村田のパワーアンプを挟むように金色のフィルタ(SAWフィルタ)が3個配置され、更にその上と左下にRFスイッチが装備されている。上側のスイッチ("H393"というロゴがある方)は、ダイバージェンスのためにアンテナを切り替えるスイッチで、下側("H320"というロゴがある方)は、送受信で回路を切り替えるもののようだ。 【RoC】

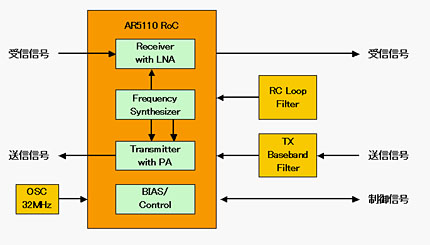

Radio on Chipを略してRoCと呼ばれるのがこのAR5110Aである。内部構造を<図2>に示すが、ご覧の通りあまり詳細は説明されていない。ただ今年のISSCC(IEEE International Sold-State Circuit Conference)における発表によれば、内部回路はSliding I/Fと呼ばれる、スーパーヘテロダインとダイレクトコンバージョンのあいの子とも言うべき回路方式らしい。基本的にはスーパーヘテロダイン方式で、中間周波数への変換を行なうが、この際の周波数を受信回路側を4GHzに、送信側を1GHzに設定したことで、外部のVCO回路を不要にしたほか、特に送信側に外部フィルタを集積する必要をなくしたことが大きいとされている。実際、回路上の部品を見てみるとSAWフィルタはアンテナとAR5110Aの間だけに存在し、その先は全てLCRを使ったフィルタ回路のみとなっている。 なお、ISSCCにおける発表では、IEEE 802.11a規格に従った場合の送信出力の評価値は17.8dBmとなっており、スペックの22dBmに及ばない。パワーアンプを外付けするのも仕方ないだろう。

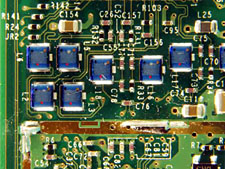

【フィルタ回路】

ここに示すのは全体の一部であるが、チップコンデンサと表面実装タイプのコイルが所狭しと並んでいるのが判る。基本的にはIF周波数をうまく設定しているため、イメージ信号(スーパーヘテロダイン方式で発生する偽信号。これを取り除いてやらないと無駄な輻射が発生する)がチップ上のフィルタで除去できるため、外部に用意するフィルタはLCR回路だけで構成できるようになっており、結果的にパッケージサイズやコストを抑えられるというのがAtherosの謳い文句である。 【MAC/ベースバンド】

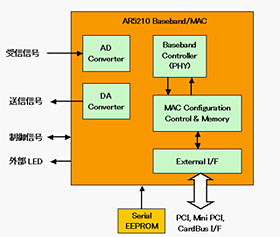

ベースバンドチップセットとMACを集積したのがこのAR5210である。内部構造は<図3>に示すとおりだが、例えばIntersilのPrismⅢでもここは1チップ化されているなど、それほど難易度は高くない。高速転送を前提に、PCI/MiniPCI/CardBusインターフェイスを用意しているのも当然であろう。加えるなら、内部に必要なメモリ類は集積しているため、外部にバッファメモリの類を用意する必要がないのは(最近のチップとしては当然なのだろうが)長所の一つと数えても良いだろう。なお図には出てないが、構成を変更することでGPIO(General Purpose I/O)インターフェイスを使うこともできる。

【シリアルEEPROM】 唯一外部に必要なメモリがこれである。利用されているのはSTMicroelectronicsのM93C66-Wで、チップの動作モードやMACアドレスなど、必要なパラメータをAR5210に供給するためのものである。

■というわけで というわけで、第3回目のIEEE 802.11b対応カード「WN-B11/PCM」とは打って変わってシンプルな構成になっている事がわかる。ただ、シンプルなのはAR5000の集積度の高さによるものなのは間違いなく、今年のISSCCでAtheros Communicationと米Stanford Universityが共同で行なった発表に大挙して聴衆が詰め掛けたのも無理ないことである。これまでCMOSプロセスでこうしたRFを取り扱うのは殆ど不可能と思われていただけに、これを可能にするとここまで回路がここまで簡単になるというのは驚異的なことである。「AtherosはTSMCのCMOSプロセスを知り尽くしている」(国内某メーカーの関係者)という賛辞もあがるほど先進的なチップを搭載したこの製品が、2万円未満で入手できる現状はものすごく幸せなのかもしれない。 (2002/04/25) |

|

| Broadband Watch ホームページ |

| Copyright (c) 2002 impress corporation All rights reserved. |